Public

# ASML

#### Integration of a Fab Cyber Physical System The marriage of two digital twins

Tom Hoogenboom,

ASML, System Engineering

SASG, Eindhoven June 4th, 2019 v1

int. ref. D735590

ASHL

**ASML**

Slide 2

Summary

**Topics**

ASML is a patterning/lithography company Chips are made with data

Two digital twins are horizontally and vertically integrated

Horizontal integration is the most challenging

**ASML**

Slide 3

Summary

ASML is a patterning/lithography company

Chips are made with data

Two digital twins are horizontally and vertically integrated

Horizontal integration is the most challenging

# It's hard to imagine a world without chips

Public Slide 4 Q4 2018

### Example: Self-driving truck (expected between next year and 2025)

**ASML**

#### Founded in 1984 as a spin-off from Philips

Public Slide 6 Q4 2018

### A global presence with >23,000 employees

Public Slide 7 Q4 2018

# Our key locations

Public Slide 8 Q4 2018

#### All major chipmakers are our customers

Public Slide 9 Q4 2018

| Company                              | Segment            | 2018 capex<br>(est., \$B) |

|--------------------------------------|--------------------|---------------------------|

| SAMSUNG                              | Foundry + Memory   | 24.0                      |

| intel                                | Integrated Devices | 14.0                      |

| tsinc                                | Foundry            | 11.0                      |

| SK hynix                             | Memory             | 11.0                      |

| Micron                               | Memory             | 8.5                       |

| TOSHIBA <i>ivid</i> Western Digital' | Memory             | 7.3                       |

|                                      | Foundry            | 4.5                       |

| SMIÇ                                 | Foundry            | 1.9                       |

| UMC                                  | Foundry            | 1.1                       |

| SONY                                 | Others             | 1.0                       |

| Others                               |                    | 30.7                      |

| Total                                |                    | 115.0                     |

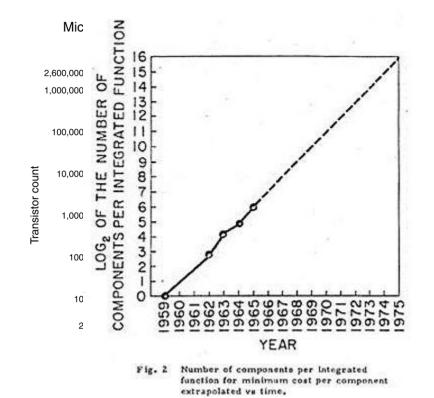

#### Driving the semiconductor industry: Moore's Law

Public Slide 11 Q4 2018

Gordon Moore (1965): Number of transistors per chip doubles every year.

Later adjusted to two years, the trend has held for more than four decades.

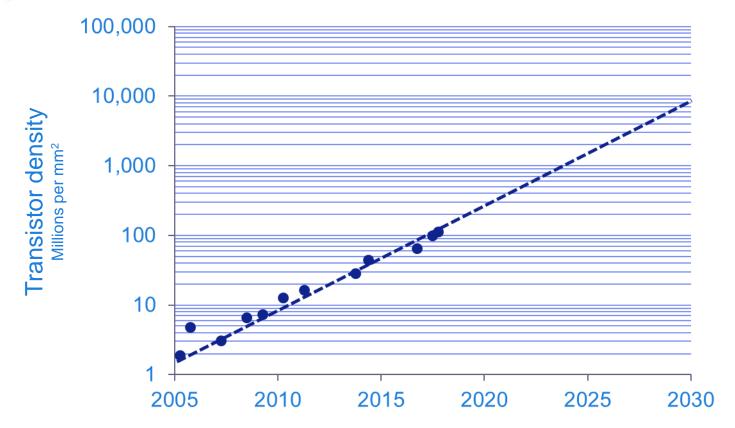

#### We see this trend continuing beyond the next decade Our industry is moving towards 1 billion transistors per mm<sup>2</sup>

ASML

Public Slide 12 Q4 2018

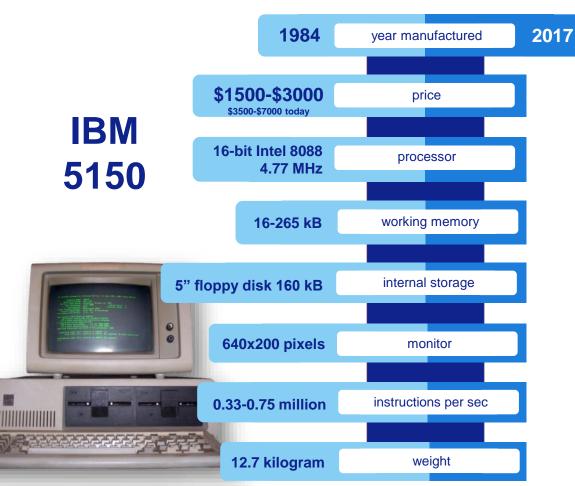

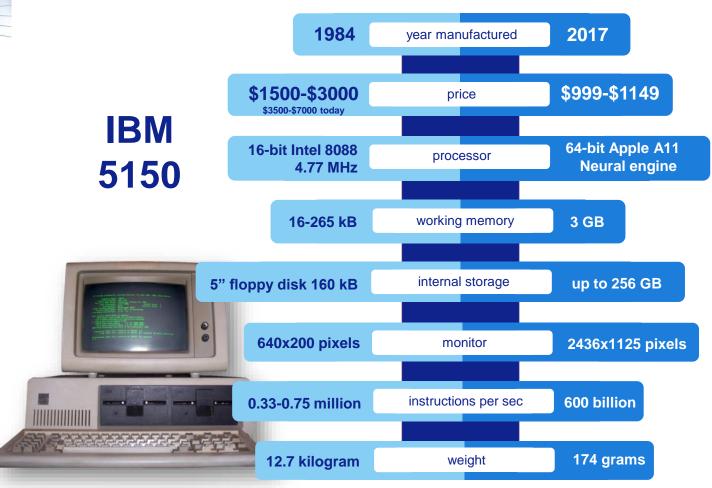

#### Moore's Law powers innovation and lowers cost

Apple iPhone X

ASML

Public Slide 13

Q3 2018

### Moore's Law powers innovation and lowers cost

ASML

Public Slide 14 Q3 2018

Apple iPhone X

### Keeping up with Moore's Law

Public Slide 15 Q4 2018

**1984** PAS 2000 ASML's first stepper

#### 2015 TWINSCAN NXT:1980Di Our most advanced

ASHL

immersion system

2018 TWINSCAN NXE:3400B High volume EUV system

ASML

Public Slide 16

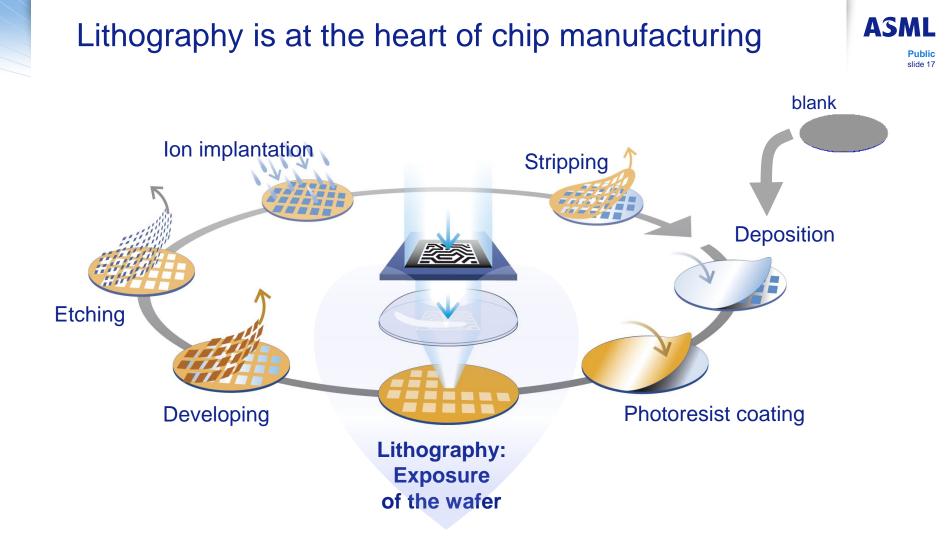

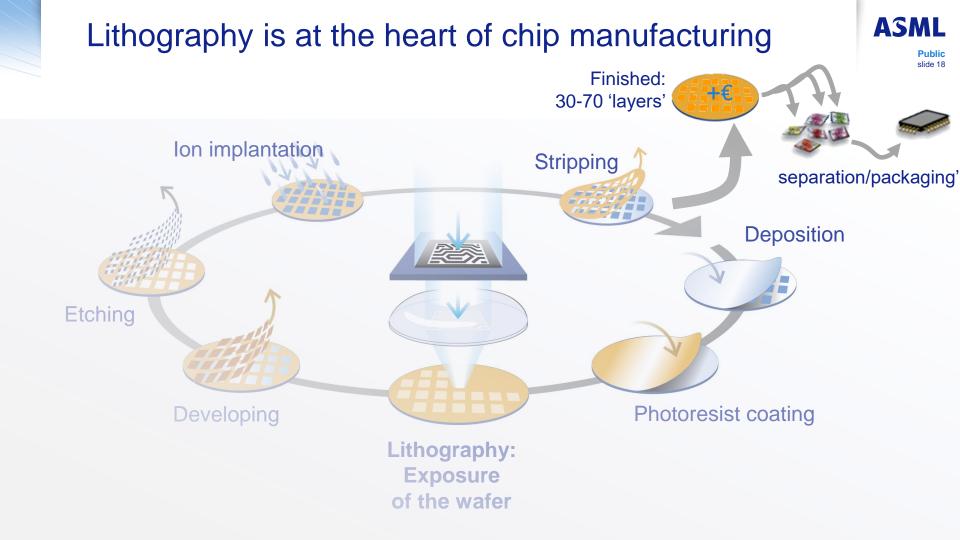

#### Summary

## ASML is a patterning/lithography company

Chips are made with data

Two digital twins are horizontally and vertically integrated

Horizontal integration is the most challenging

# Keeping up with Moore's Law

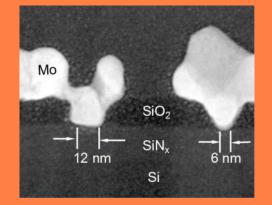

# Structure in a chip: 6 nanometer detail

#### **1984** PAS 2000 ASML's first stepper

#### 2015 TWINSCAN NXT:1980Di Our most advanced immersion system

2018 TWINSCAN NXE:3400B High volume EUV system

## Keeping up with Moore's Law

Wavelength: 13.5 nanometers

Resolution: ≤ 22 nanometers

Overlay: 1.0 nanometers

> Wafer size: 300 mm

Productivity: 125 wafers per hour

**1984** PAS 2000 \SML's first steppe

#### 2015 TWINSCAN NXT:1980Di Our most advanced immersion system

ASMIL

2018 TWINSCAN NXE:3400B High volume EUV system Public Slide 20 Q3 2018

ASML

# Control at nm level is really fine-grained

1 mm motion on scale of The Netherlands (300 km Ø)

1:300,000,000

**ASML**

Public Slide 21

# Control at nm level is really fine-grained

1 mm motion on scale of The Netherlands (300 km  $\emptyset$ )

1:300,000,000

1 nm motion on scale of wafer (300 mm Ø)

1:300,000,000

Public Slide 22

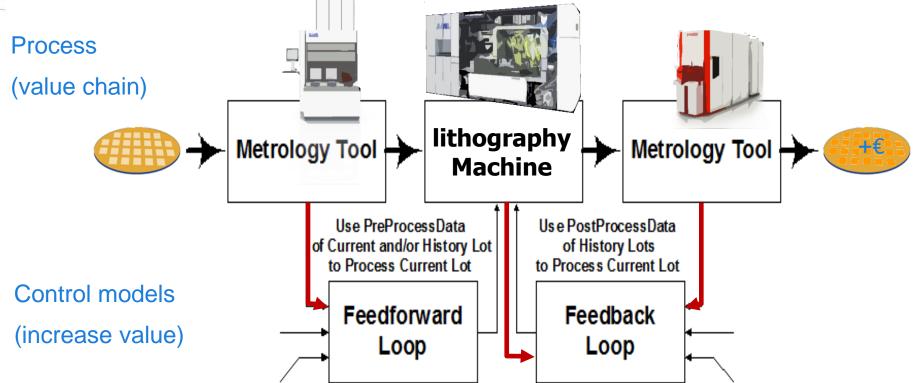

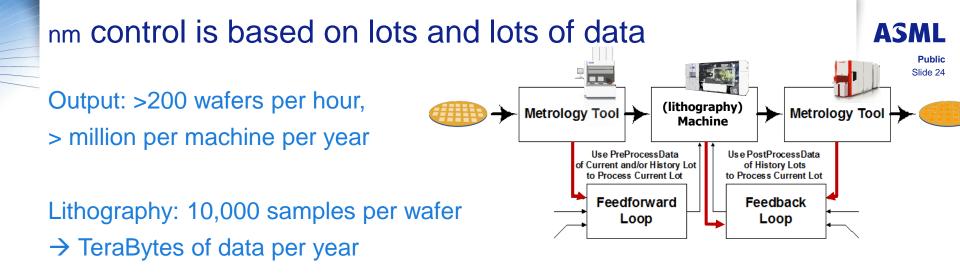

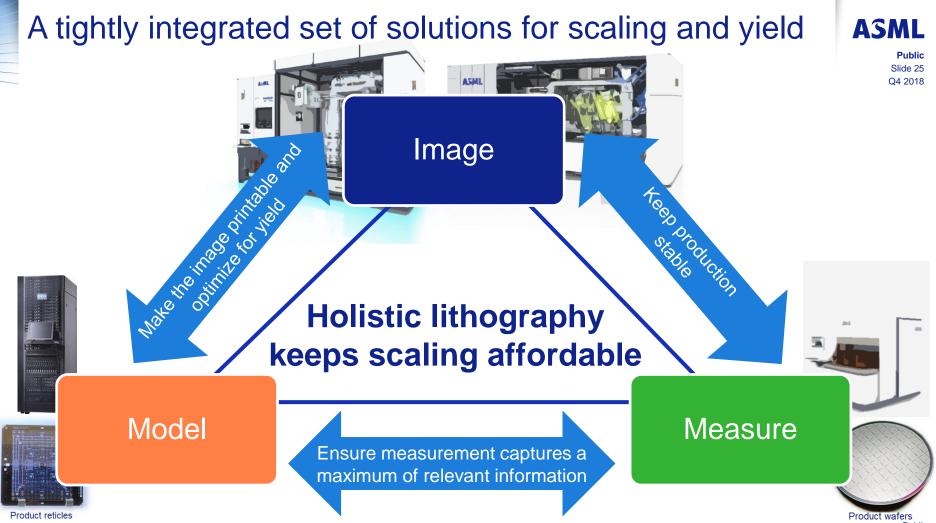

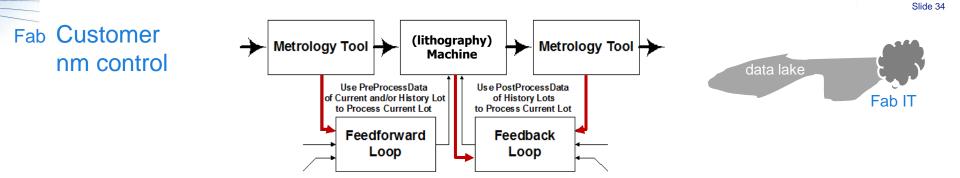

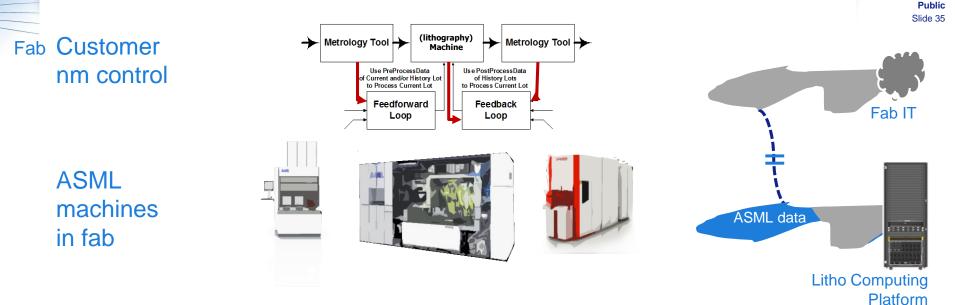

# nm control is about integration of metrology (measuring)

Public Slide 23

ASML

Metrology tool: 100-10,000 samples per wafer → TeraBytes of data per year

Fabs use this to control every square  $mm^2$  of every wafer: Input per wafer: 100,000 x 6 axis = 600,000 inputs/wfr

Public

ASML

Public Slide 26

#### Summary

ASML is a patterning/lithography company

Chips are made with data

Two digital twins are horizontally and vertically integrated

Horizontal integration is the most challenging

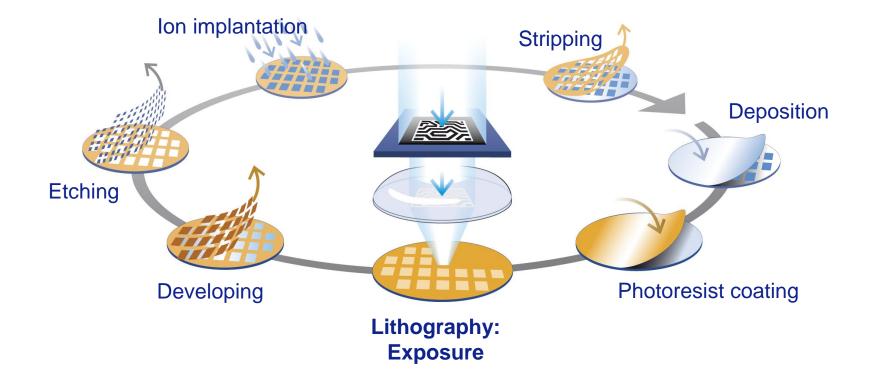

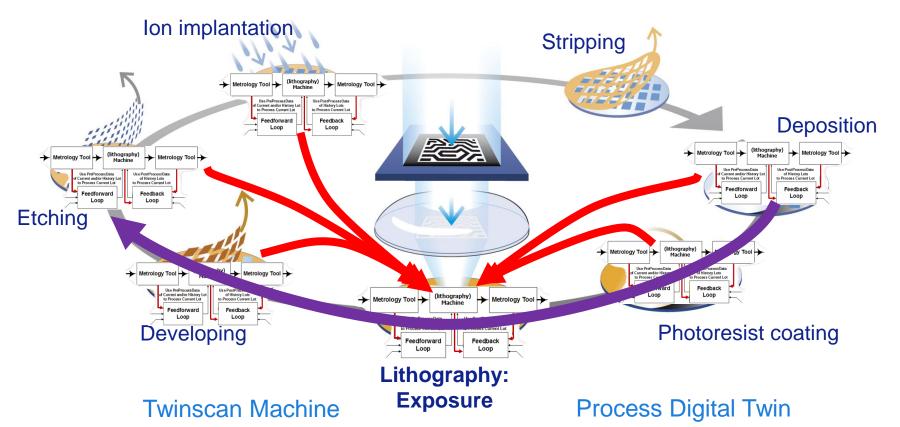

### Lithography value chain: 700+ steps

ASML

Public slide 27

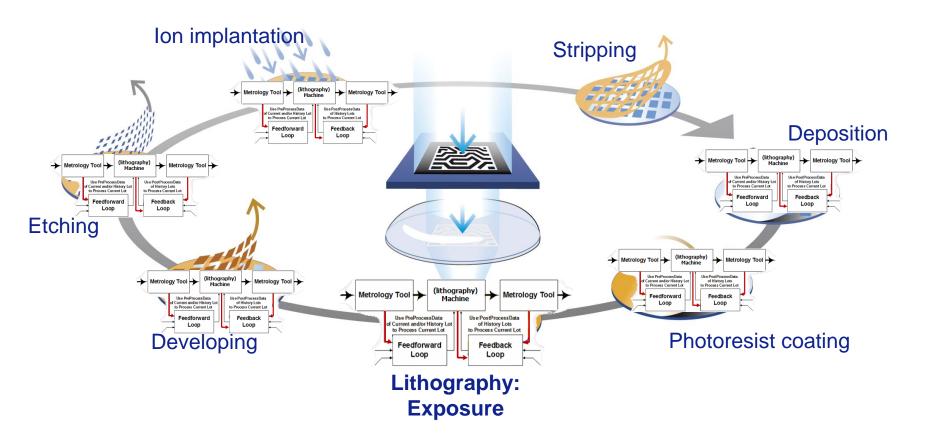

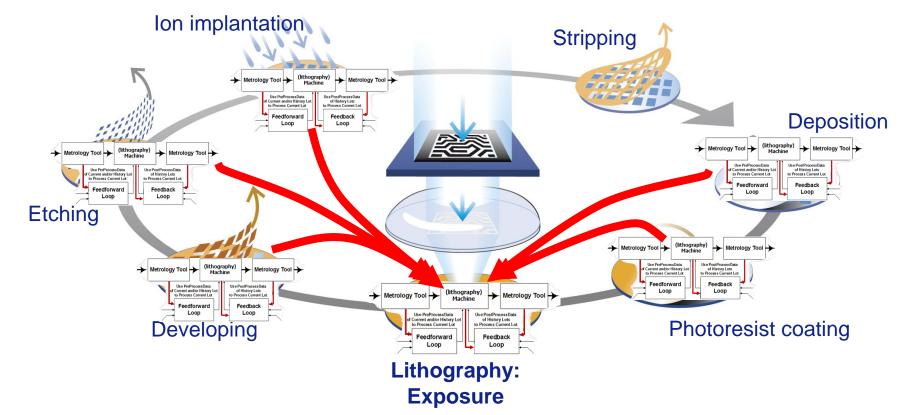

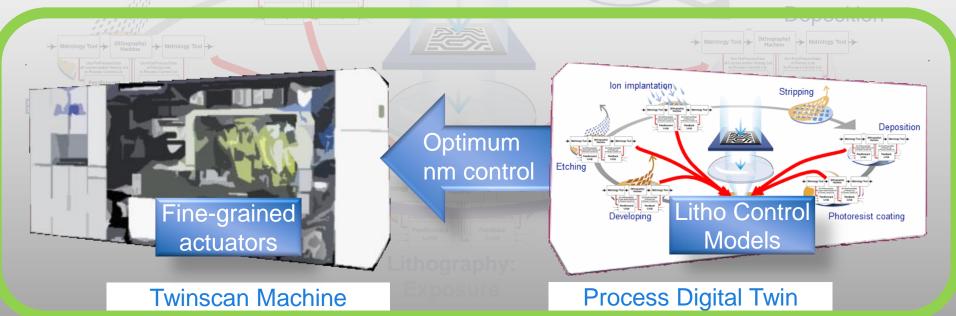

# Lithography is horizontally integrated in 700+ steps

#### Lithography is horizontally integrated in 700+ steps Upstream and down stream steps feed data into our litho models

ASML

Public

slide 29

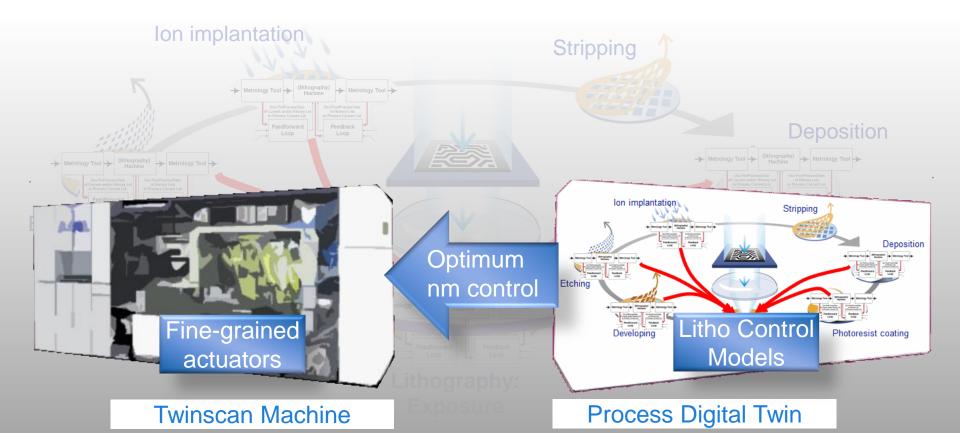

Lithography is horizontally integrated in 700+ steps Upstream and down stream steps feed data into our litho models so the patterns 'after etch' come out almost nm-perfect. ASML

Public

slide 30

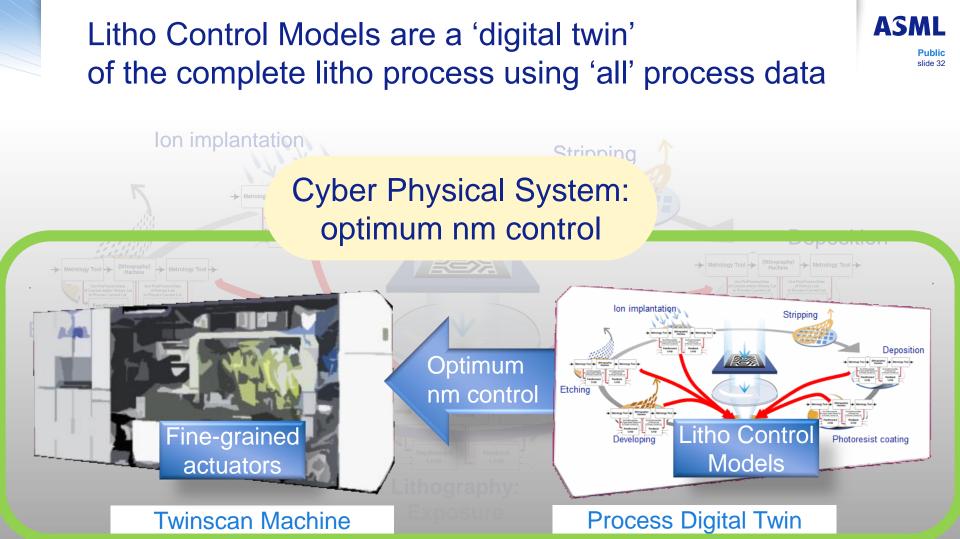

# Litho Control Models are a 'digitital twin' of the complete litho process using 'all' process data

ASML

Public

slide 31

ASML

Public Slide 33

#### Summary

ASML is a patterning/lithography company

Chips are made with data

Two digital twins are horizontally and vertically integrated

Horizontal integration is the most challenging

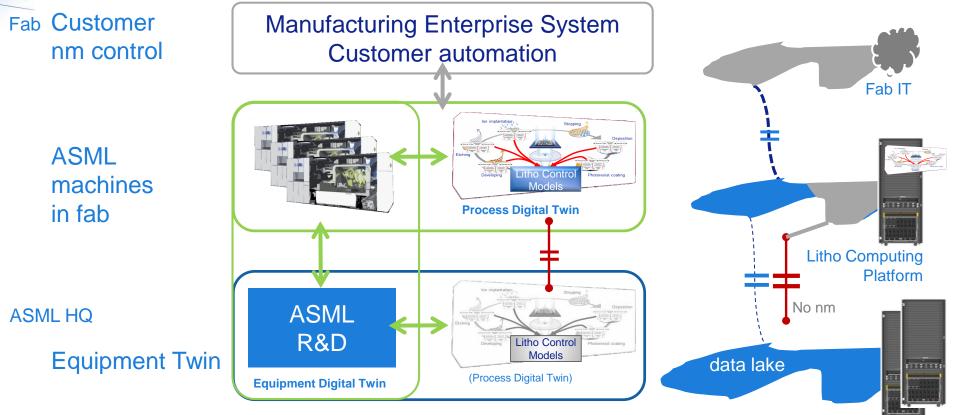

#### Vertical 'integration': separate data lakes fab/ASML

ASML

Public

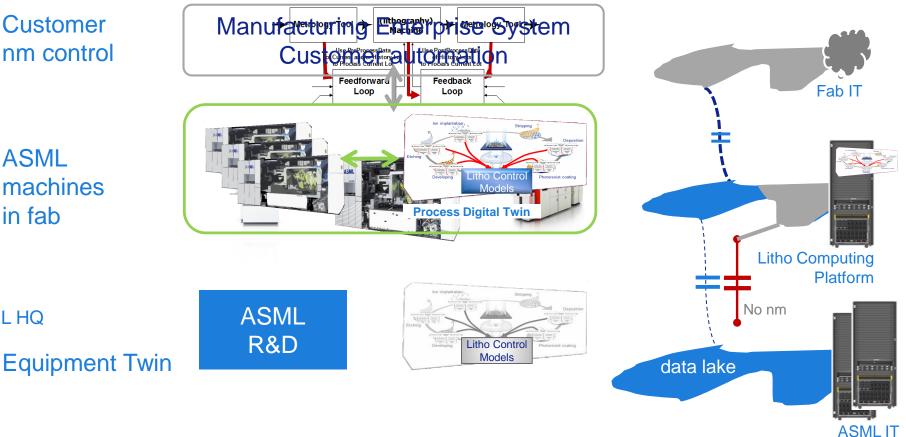

## Vertical 'integration': separate data lakes fab/ASML

**ASML**

## Vertical 'integration': separate data lakes fab/ASML

Public Slide 36

**ASML**

ASML HQ

Fab Customer

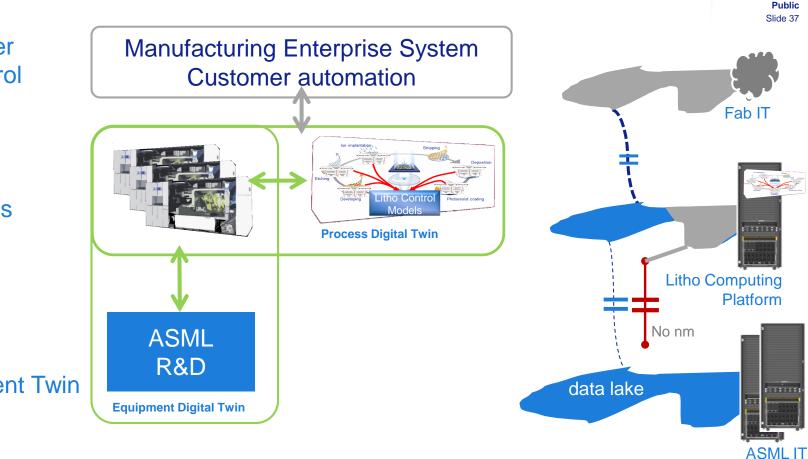

# Two digital twins, not yet happily married

Fab Customer nm control

> ASML machines in fab

ASML HQ

Equipment Twin

Public

ASML

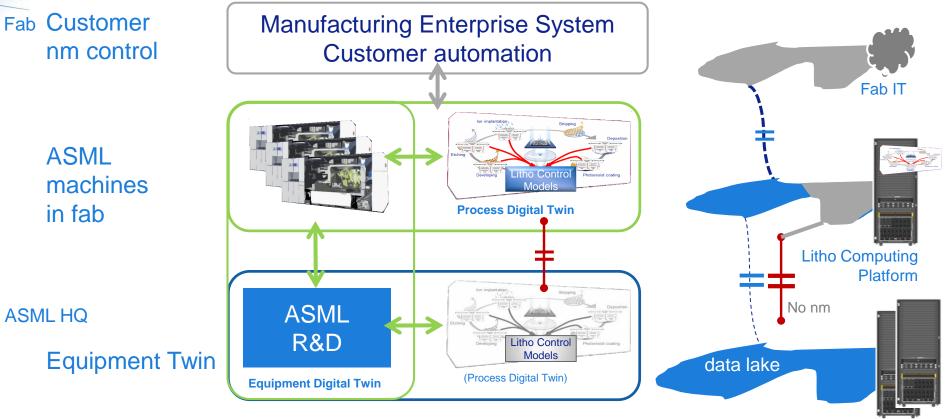

# Two digital twins, happily married

Public Slide 38

**ASML**

Public

ASML IT

ASML

Public Slide 39

#### Summary

ASML is a patterning/lithography company

Chips are made with data

Two digital twins are horizontally and vertically integrated

Horizontal integration is the most challenging

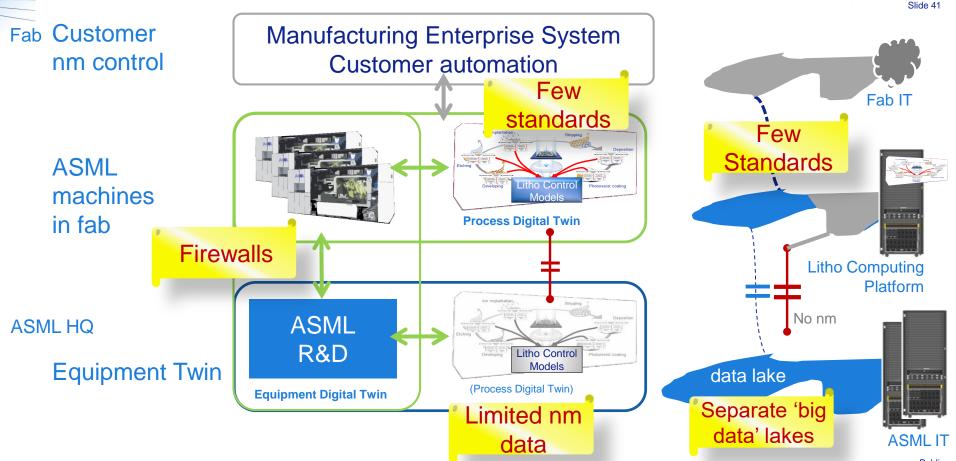

## Vertical integration is challenging but doable

Public Slide 40

ASML

Public

ASML IT

#### Vertical integration is challenging but doable

Public

ASML

Public

#### Horizontal integration is the most challenging

- This is our customers' expertise and value chain  $\rightarrow$  team up

- ASML does not (can not) get all nm data  $\rightarrow$  link data lakes

- nm control implies ppb (part per billion) accuracy levels: subtle trends, 1:1,000,000 incidents → access to 'all' data needed

Public slide 42

ASML

Public Slide 43

Horizontal and vertical integration happens, driven by economics (i.e. nm gain)

Standards for vertical integration are essential to allow cross-enterprise cooperation to work

Horizontal integration – via teams – requires a way to have interoperable CPS'es and Data Lakes

**ASML**

Public Slide 44

#### Recap

ASML is a patterning/lithography company

Chips are made with data

Two digital twins are horizontally and vertically integrated

Horizontal integration is the most challenging